안녕하세요? DRAM 소자와 공정에 대해 정리해 두었습니다. 면접이나 업무 보실 때 참고하세요~

사실 간단한 DRAM의 동작원리는 워낙 쉽게 설명한 동영상도 많기 때문에, 생략하고 원론적인 이야기로 넘어가겠습니다.

1. DRAM이 만들어지는 웨이퍼

왼쪽그림이 DRAM 웨이퍼입니다. 검은 선으로 와플모양으로 구획이 나눠져 있습니다. 왜 저렇게 생겼을까요? 바로 포토 공정의 한계 때문입니다.

DRAM은 정말 작습니다. Lithography 공정은 마스크(Recticle)에 투과한 빛을 모아 패터닝을 해야 하는데, 큰 웨이퍼를 한 번에 패터닝할 수 없습니다.(렌즈의 크기가 제안되고 기술적 uniformity가 어렵기 때문입니다.)

때문에 웨이퍼 전체에 한번에 빛을 쪼아 줄 수가 없고, 한지점 빛을 쪼아주고 다음지점을 쪼아주는 식으로 패터닝을 합니다.

따라서 왼쪽 그림의 웨이퍼에 검은색 선으로 와플 모양처럼 구획을 나눠놓은 게 이 패터닝을 한번 할 때 빛이 쪼아지는 곳입니다. 이러한 한 네모칸을 Shot이라 합니다.

Shot 내부를 자세히 보면 또 여러 구획으로 나눠져있습니다.(파란색 선) 이게 바로 DRAM 칩 하나하나를 나누기 위해 쪼개논 겁니다. 이 파란색 네모 하나를 Die라고 합니다.

Die 내부에 DRAM이 동작하는 부분을 보면 커패시터로 실제 정보를 저장하는 셀로 이루어진 BANK(F표시가 된: 실제 F표시가 된 게 아니고 아래에서 설명할 모양으로 되어있습니다.) 구획과 이 정보를 제어하는 Decoder(YDEC, XDEC), 그리고 peripheral(Peri.)라는 회로로 이루어져 있습니다.

F로 표시된 BANK 영역을 먼저 보겠습니다. 바로 이 부분이 커패시터를 포함한 부분입니다. F라고 표시된 부분에 차마 그리진 못했지만 여기도 엄청나게 많은 반복된 구조로 나누어져 있습니다. 이 구획 중 하나를 들여다보면 커패시터와 트랜지스터가 마구 모여있습니다. 이 영역을 MAT라고 합니다.

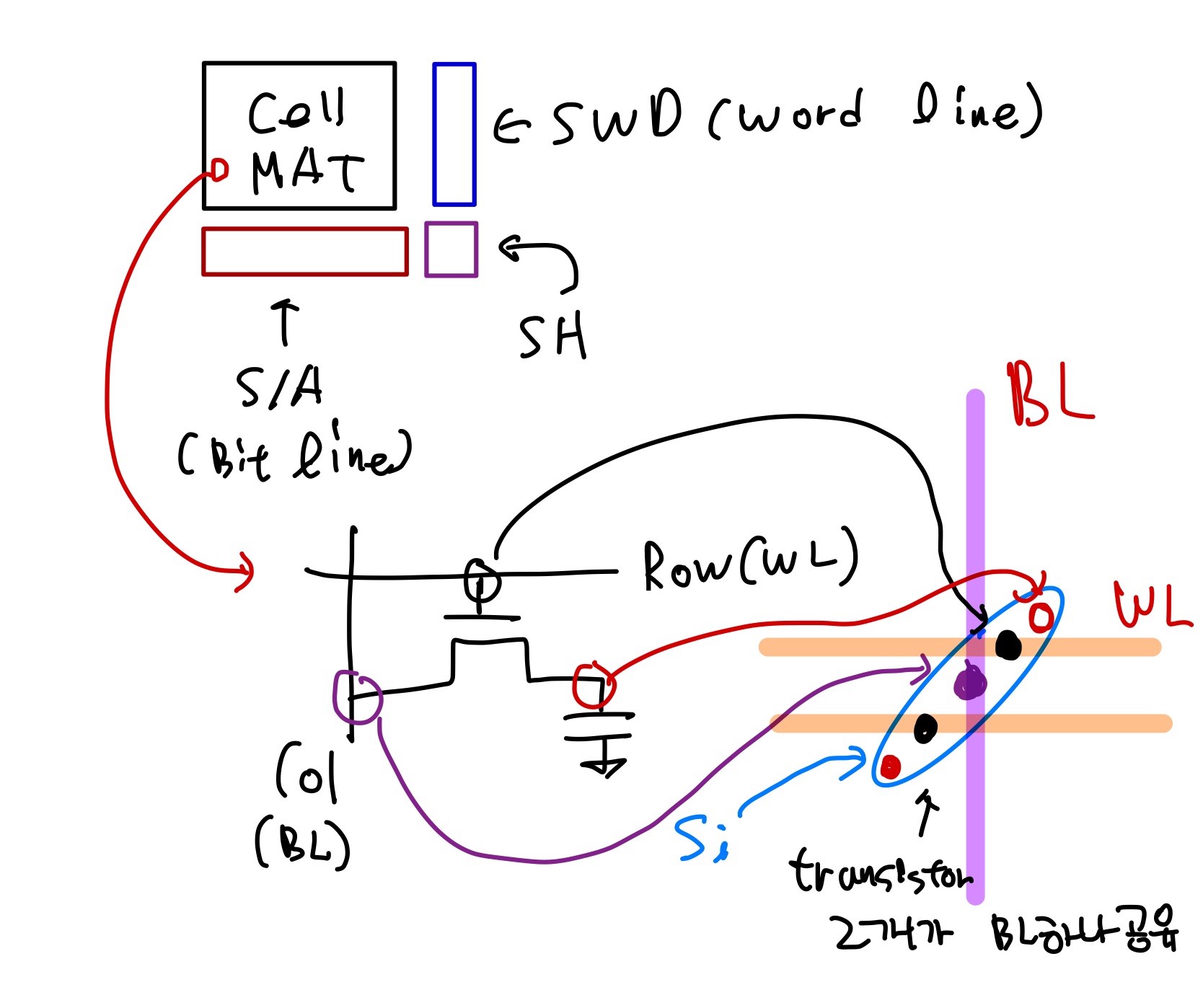

이 MAT는 Cell MAT이라는 커패시터로 이루어진 부분과, 쓰기 읽기를 제어하는 SWD(word line), 신호를 제어하는 S/A(bit line)으로 이루어져 있습니다.

이 Cell MAT에 또 반복되는 부분 중 하나를 집어보면 한 개의 커패시터와 트랜지스터 하나로 이루어져 있습니다. 이를 Cell이라 합니다.

너무 숨차게 달려왔는데, 정리를 하자면 웨이퍼를 나눠 Shot이 나오고 Shot 안에 Die가 있고 Die안에 BANK가 있고, BANK안에 Cell MAT이, Cell MAT안에 Cell이 있어 비로소 익숙한 DRAM이 나옵니다.

이 개념을 이해한 뒤 인터넷에 DRAM이라고 검색하면 나오는 아무 그림이나 봐도 어떤 구성으로 되어있는지 이해가 될 거라 예상합니다.

일반적으로 컴퓨터에 사용하는 DRAM DIMM안에 여러 개의 chip이 있고, (예를 들어 8G DRAM이라면, 1G짜리 Chip 8개) Chip 내부에는 BANK가 있고(한 chip에 16개 BANK가 있다고 가정), BANK에는 MAT이 있고, MAT안에 Cell 이 있는 구조입니다.

작은 공간에 더 많이 넣기 위해 실제 패턴은 BL(bit line)과 WL(word line)이 수직으로 배선되고 두 개의 트랜지스터가 한 개의 BL을 공유하는 형식으로 배치되어 있습니다. 이를 허니컴 구조라 하는데, 왼쪽 그림으로는 이해가 어려우니 다음 그림에서 설명드리겠습니다.

2. DRAM 소자의 배치

먼저 Bit line과 Word line을 가지고 트랜지스터와 커패시터가 어떻게 배치되어 있는지 간단하게 확인해 보겠습니다.

위 그림의 빨간색과 파란색은 Word line이고 보라색이 bit line입니다. 초록색은 S/A(Sense amplifier: 읽는 신호 증폭시켜 줌)이라고 생각하시면 됩니다. Word line은 동작을 제어한다 보시면 되고, Bit line은 전기 상태를 검출하고 주입하는 역할을 한다고 보면 됩니다. 이 구조는 뒤에서 중요하게 다시 다루겠습니다. 보시면 검은색으로 그려진 트랜지스터 두 개가 직렬로 연결되어 한 개의 Bit line을 공유하고 공유하지 않은 극에는 커패시터와 GND를 가지고 있습니다. (선글라스 낀 사람처럼 보이는데 선글라스 알 하나씩 각각 하나의 트랜지스터이고 귀 쪽은 커패시터고 GND입니다...)

먼저 위 그림의 보라색 선(Bit line)에 대해 이해하기 위해 트랜지스터 한 개와 커패시터 한 개로 구성된 구조를 보겠습니다.

DRAM의 커패시터는 가만히 놔두면 배터리가 방전된 듯, 저장되어 있는 전하가 없어지게 됩니다. 따라서 어느 정도 시간이 지나면 다시 전하를 채워줘야 하는데 이를 Refresh라 합니다. 또 채워줘야하는 경우가 있는데 읽을 때도 전자가 손실되므로 Refresh를 시켜줘야 합니다.

앞선 전 그림의 녹색 라인이 왼쪽 그림의 파란색 빨간색으로 된 회로입니다. 바로 커패시터에 저장된 신호를 읽어주는 역할을 합니다.

Vcore가 높은 전압, Vss가 낮은 전압으로 구성되어 있는데, Vss를 0V라 한다면 BL(Bit line)에는 항상 Vcore/2만큼의 전압이 걸려있습니다.

이제부터 V_BL=Vcore/2이라고 생각하면 됩니다.

커패시터에 Vcore만큼 전압이 저장된다면, V_BL보다 큰 전압이므로

$$V_{BL}+\Delta V$$

로 표기할 수 있고, 0V 만큼 전압이 저장된다면, V_BL보다 작은 전압이므로,

$$V_{BL}-\Delta V$$

로 표기될 수 있습니다.

다시 본론으로 돌아가서 만약 Vcore만큼 저장되어 있다면, WL을 ON 했을 때 /BL은 V_BL이고 BL은 V_BL+del V 이므로 파란색 위에 트랜지스터는 OFF 되고 아래 트랜지스터는 ON 됩니다. 그렇게 되면 두 파란색 트랜지스터 사이는 Vss가 되고 빨간색 위에 트랜지스터는 ON 아래 트랜지스터는 OFF가 됩니다. 이렇게 BL과 Vcore가 연결되게 되어 BL은 Vcore가 되어 커패시터 안에 Vcore가 저장되어있다는 것을 안정적으로 증폭 할 수 있고, 커패시터에 Vcore를 다시 저장해 줄 수 있습니다. 즉 읽기위한 증폭과 Refresh를 동시에 할 수 있습니다. 이를 전압 관점으로만 살펴본다면, 본 그림의 회로 아래에 있는 그래프를 보시면 됩니다. 초록색이 BL에 전압인데, RAS가 잠시 감소하며 읽기 동작을 위한 Active에 대한 신호를 줍니다. 즉 WL이 ON됩니다. 신호가 들어가면 회로 동작을 하여 커패시터에 저장된 값이 BL과 charge share를 하여 신호가 살짝 올라가고 회로가 안정화되어 BL은 Vcore가 되고, /BL은 Vss가 됩니다. 여기서 쓰기 동작까지 할 수 있는데, CAS가 잠시 감소하면 Yi라는 회로가 동작하여, BL에 신호가 들어가 쓰기를 수행합니다. 그러고 다시 대시상태인 BL은 V_BL로 돌아갑니다. 여기서 신호가 중요한데, 읽기 시간을 보통 t_RCD, 쓰기 시간을 T_WR로 부르고 둘의 총합을 t_RC라 합니다.

이제 공정을 봐야겠죠?? 공정은 바로 "DRAM 디램 공정"(링크) 여기에 있습니다!! 링크를 눌러주세요~!

'메모리' 카테고리의 다른 글

| HBM (High Bandwidth Memory) (0) | 2024.05.12 |

|---|---|

| DRAM 디램 공정 (10) | 2022.03.14 |