| 가정 | TSV (through silicon via), Frame Buffer (프레임 버퍼), AWORD(Address Buffer) / DWORD(Data Buffer), MISR, implicit precharge, pseudo channel, DRAM 디램 공정, DRAM 디램 소자 동작 및 구성 |

| 참고논문 | |

| 응용 |

↑파란 박스의 글자를 클릭하시면 가정과 응용으로 넘어 가실 수 있습니다!!

메모리 반도체의 한 종류인 HBM(High Bandwidth Memory)는 축약어 그대로 Bandwidth가 높은 메모리입니다.

여기서 Bandwidth의 Band는 신호가 왔다 갔다 하는 통로이고, Width는 넓이 입니다. 신호가 왔다갔다 하는 통로가 넓으면 당연히 더 많은 신호가 왔다갔다 할 수 있겠죠? 보통 HBM을 설명할 때 비유상으로는 일 차선 도로에서 8차선 고속도로 등으로 표현하는 이유도 이 이유입니다.

HBM이 다른 메모리 보다 Bandwidth를 높일 수 있는 이유는 말 그대로 전선의 개수를 몇 천 개 수준으로 많이 만들었기 때문입니다. 참고로 GDDR5의 전선 수는 32개입니다. 물론 요 몇천 개(HBM3기준 1024, 4 기준, 2048개의 In Out 선(I/O라고도 부릅니다.))를 작은 한 개의 Chip에서 감당하기 힘드므로 선을 TSV라는 기술을 이용해 여러 개를 Chip을 쌓아서 만듭니다.

보통 HBM을 묘사할 때 Chip이 여러개 쌓여있는 모양 때문에 헷갈릴 수 있는데, HBM만 Chip을 여러 개 쌓지 않습니다. 다른 HBM이 아닌 DRAM들도 TSV를 이용해 쌓고, 이를 3DS 메모리라 합니다. 이는 순전히 Memory 용량을 높이기 위함이지, Bandwidth를 높이기 위해 쌓는 것이 아닙니다.

따라서 HBM을 이해하려면 적층 하는 TSV기술보다 내면에 있는 회로 및 구성에 대해 이해해야 합니다.

보통 AI가 관심이 높아지며 HBM이 각광을 받고 있긴 하지만, HBM이 AI를 위해 만들어진 제품도 아니고, AI를 실제 구동하는 메모리도 아닙니다. 단순히 HBM에 전송선로가 많아 AI 알고리즘이 감당해야 할 많은 양의 데이터를 빠르게 불러오고 입력하는데 용이하기 때문에 사용되는 단순한 이유 때문입니다.

현재 HBM은 JEDEC이라는 국제표준화 기구에서 작성된 문서를 따라서 제작되어야 합니다.(이에 반발하여 여러 업체(보통 AMD, MS(broadcom), Nvidia에서는 본인 마음대로 만들 수 있는 Custom HBM이라는 것도 요청 중이긴 합니다.-커스텀 HBM이라 검색하시면 많은 기사가 있으니 확인하세요)

이제 JEDEC에서 정한 건 크게 HBM의 총 높이, TSV, IEEE1500 규격, Direct Analysis, PHY 등이 있습니다. 앞서 서술해논 내용을 알기 쉽게 그림으로 정리해보겠습니다.(https://www.anandtech.com/show/9969/jedec-publishes-hbm2-specification 라는 사이트에서 그림이 이쁘게 정리되어있어 그림을 가져와 보겠습니다.)

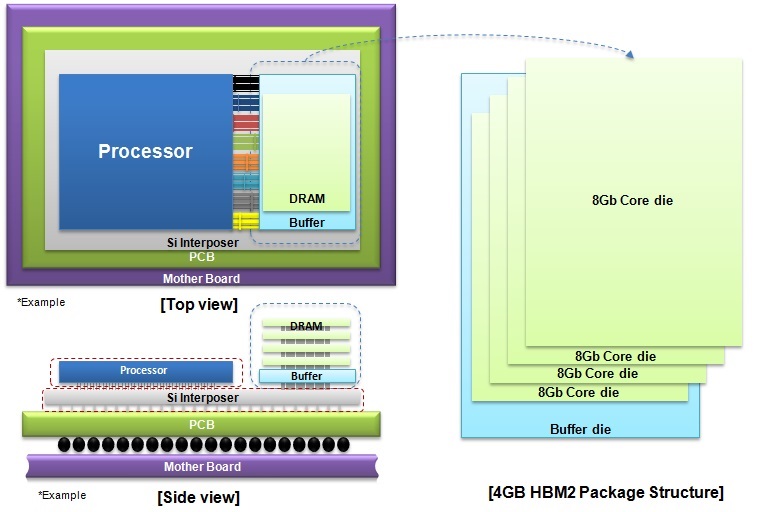

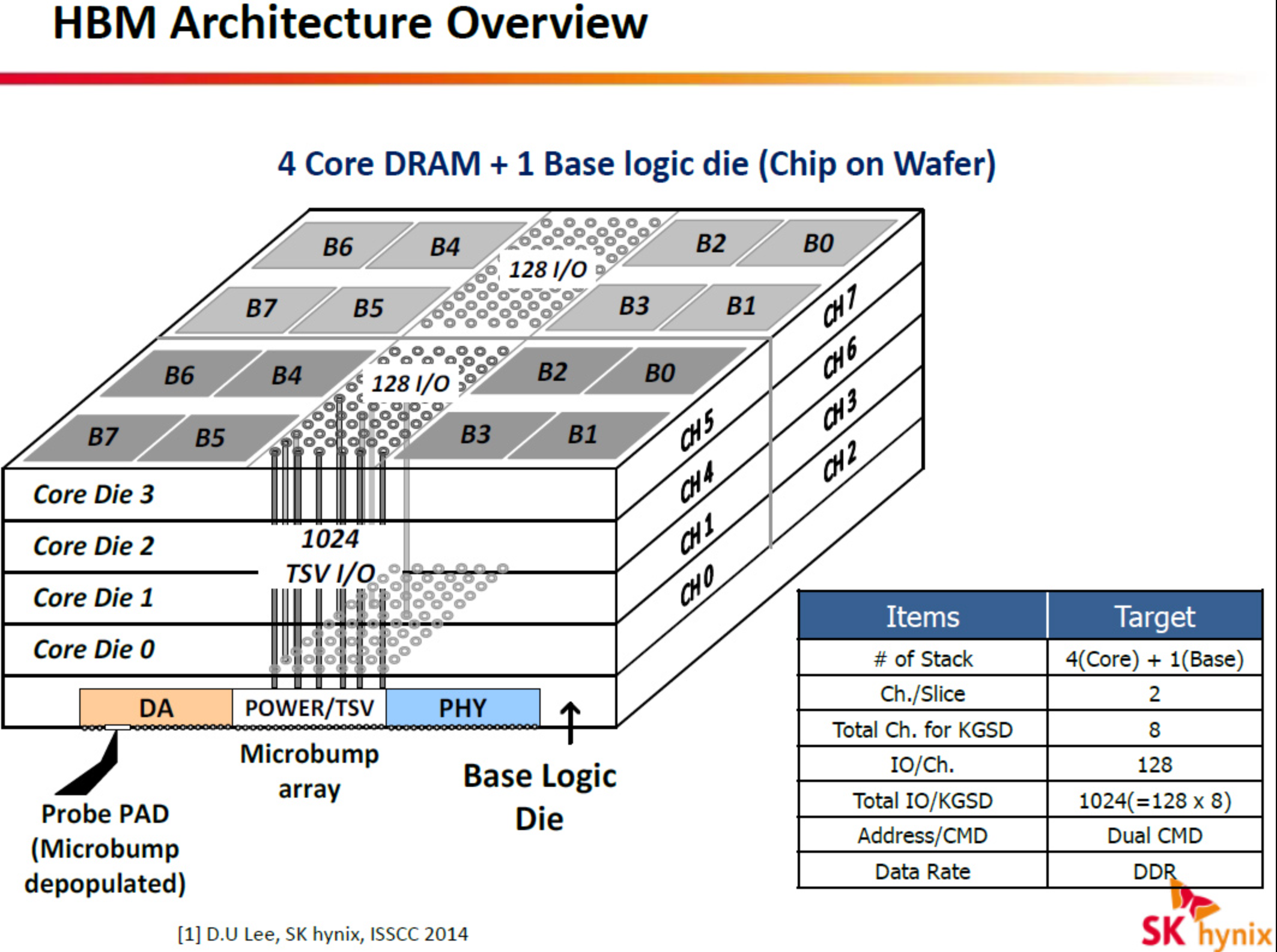

실제 HBM이 배치되는 그림입니다. 여기서 Processer는 일반적으로 알고있는 GPU라고 보시면됩니다. DRAM과 Buffer라는 부분이 HBM입니다. Core Die는 실제 메모리를 저장할 수 있는 Cell(커패시터)가 들어가 있는 Chip이고, Buffer Die는 회로만 들어가 있는 Chip입니다. Buffer Die는 다양한 용어로 표현되는데, Logic die, Base die등 이름이 붙습니다.

Buffer Die에는 Process랑 연결시켜주는 PHY라는 부분이 있고, Core Die의 통신을 제어하는 회로가 있고, Core Die와 연결하는 TSV라는 회로와 TEST를 할 수 있는 DA라는 부분이 있습니다.

위 그림에서는 Buffer Die 위에 4개의 Core Die가 올라갔는데, 위에 4개 단위로, 4개, 8개, 12개, 16개가 올라가게됩니다. 이를 제품으로는 4hi-HBM, 8hi-HBM, 12hi-HBM, 16hi-HBM이라고합니다. 4개단위로 올라가는 이유는 Buffer Die가 병렬로 각각의 Core die를 계산하는데 4개의 Channel을 사용하고 1 Channel당 한개의 Core를 쓴다고하면(정식명칭으로는 Slice라고 사용하나 이해를 위해 Core라고만 하겠습니다) 4개의 Core Die가 필요합니다. 따라서 4개 단위씩 쌓게됩니다. 참고로 요 4개를 묶어 Rank라고합니다.

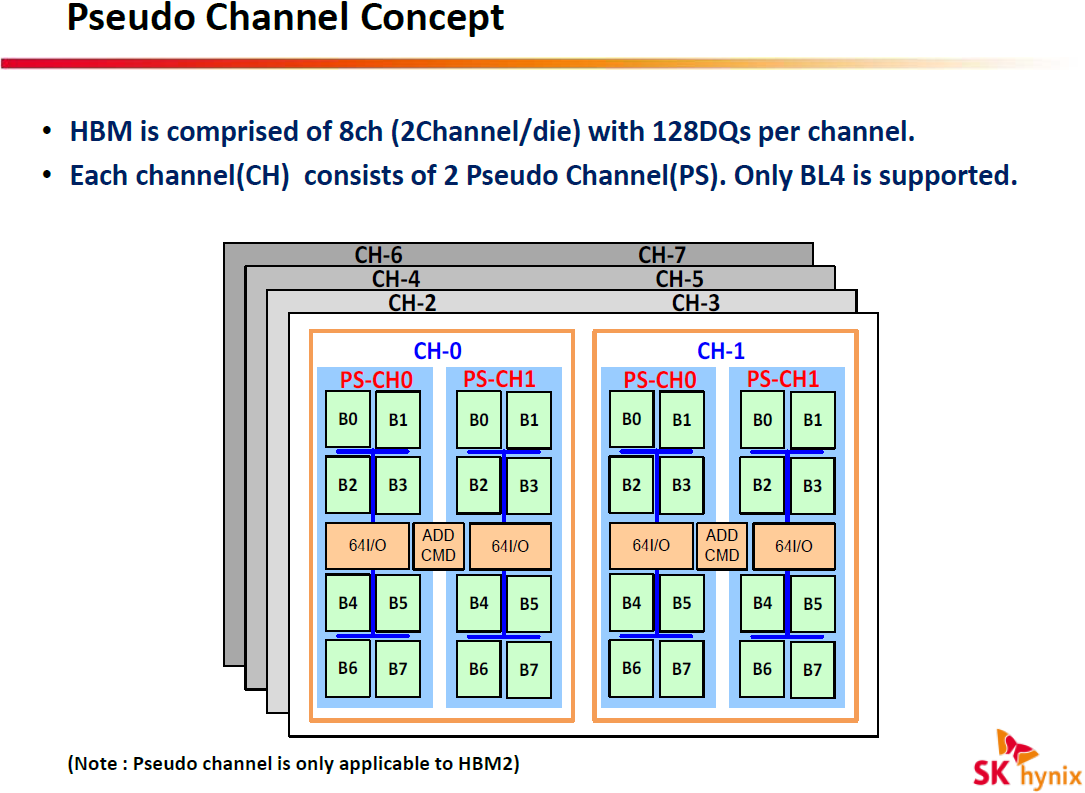

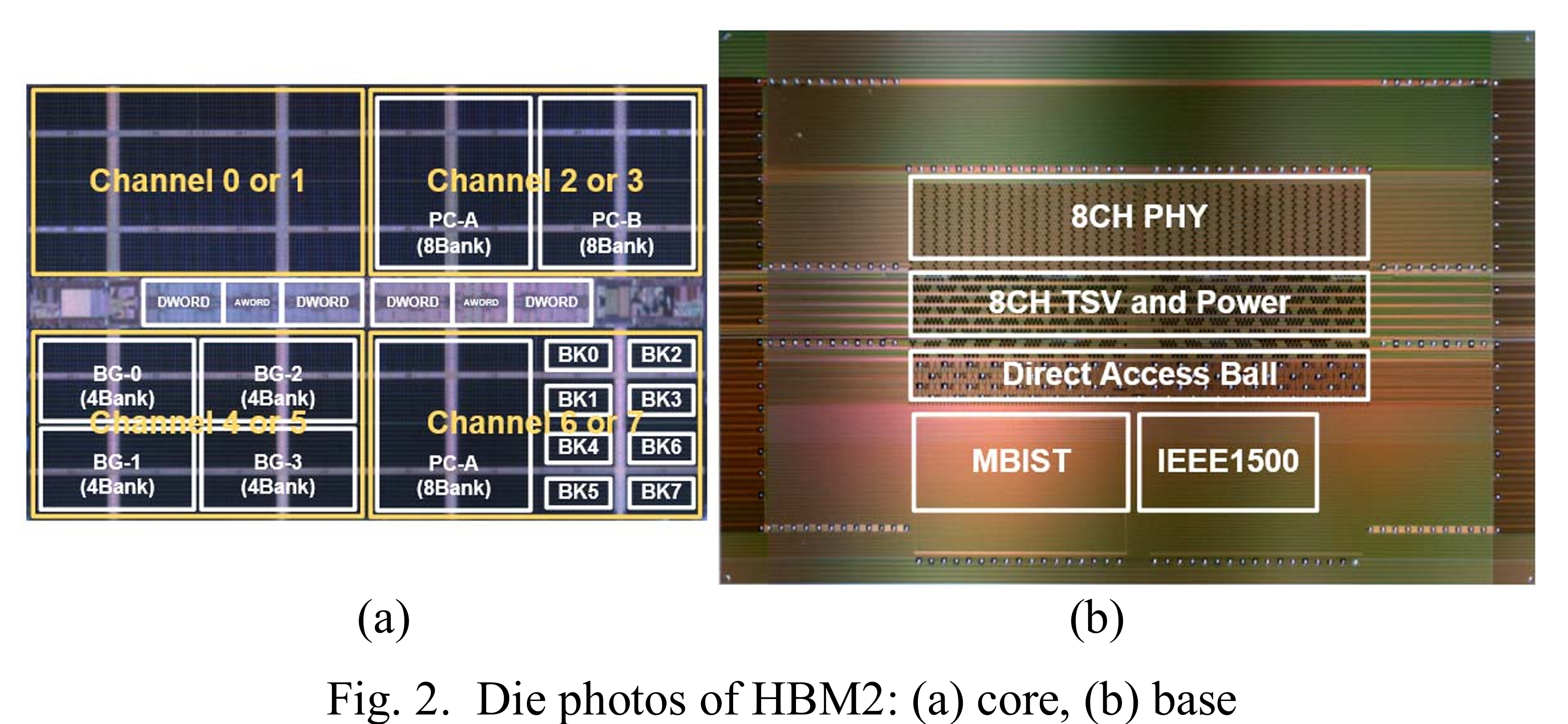

Core Die 하나는 요렇게 생겼고 CH는 Channel이라는 뜻입니다. 요 제품은 한개의 Chip에 2개의 Channel이 있네요. 위 그림에서 Pseudo Channel이라는 단어가 있는데, 이는 Channel 한개를 2개로 또 쪼개놓았다는 의미입니다. HBM에 기본적인 구조외에 이런 내용이 엄청나게 많은데 모두 목적은 같습니다. 신호를 하나보내는 동안 신호가 간섭받지 않기 위해 어느정도 시간을 부여하는데, 이런 시간이 얽히고 설켜서 아무것도 하지않은 빈시간이 존재합니다.(Bubble이라 합니다) 이런 빈 시간을 어떻게든 활용하기 위해 여러 트릭을 사용하는 내용입니다.

ADD는 Adress라는 의미이고, CMD는 Commend라는 의미로 메모리를 읽기위해 저장된 커패시터의 주소를 찾아 읽는 구조를 나타낸 겁니다. HBM은 특이하게 Address의 신호를 AWORD, 메모리 정보를 DWORD라고 사용합니다.

다음 논문의 이미지는 HBM의 logic die의 이미지입니다. 앞서 언급했듯 PHY는 GPU와 연결되는 부분으로 AWORD(address 전송)과 DWORD(데이터 전송)이 오가는 영역이고, MBIST는 HBM 자체가 self test하여 Stack 했을때 SOC, Interposer에 접합했을 때 문제가 있는지 확인하는 기능을 갖고있습니다. 다시말해 IEEE1500을 setting해서 test 동작을 설정하게됩니다. 또한 자체 평가에서 불량난 Cell을 확인해서 내부적으로 수리할 수 있도록 하는 기능도 진행합니다. 제조사마다 독자적인 test mode도 만들어서 집어넣을 수 있는데 얼마나 잘 짜냐에 따라 해당 제조사의 IP가 되게됩니다. IEEE1500은 JEDEC 규약상 필요한 Test를 집어놓는 것으로 Test 전반을 제어하는 회로입니다. 사실 대부분은 Inerconnection과 cell을 수리하는데 집중합니다. IEEE내에 유명한 회로로는 해당 회로에 MISR라는 회로가 있는데, SOC가 문제인지 HBM이 문제인지 배선이 문제인지 알려주는 회로입니다. MISR는 주로 SOC 랑 연결이 잘 되어있는지 내부 계산을 하는데 쓰입니다.(Bump가 잘 붙어있는지(살짝붙어있으면 속도가 느리므로)) Direct Access Ball은 HBM을 제어하는 Control logic이 여기에 들어가 있으며 제조사에서 test할때 쓰이는 회로입니다. 따라서 동작을 할때는 PHY -> DA -> TSV -> Core die(data)로 진행되며, test를 할때는 PHY(DA) -> MBIST -> IEEE1500 -> DA -> TSV -> Core die(data)로 진행됩니다. Test하는 회로가 굳이 3개로 나눠져있는 이유는 PHY 영역을 붙이면 때서 팔수가 없기 때문에 팔기전 test하는데 Direc access 영역만 test를 하기 때문입니다.

마지막으로 TSV를 알아보기위해 https://www.kitguru.net/components/graphic-cards/anton-shilov/sk-hynix-confirms-mass-production-of-first-gen-hbm-memory/의 사진을 가져왔습니다. 여기서는 Buffer die를 Base Die라고 표현했는데, 앞서 언급했듯, GPU와 연결하는 PHY와 회로가 정상적으로 동작하는지 확인하는 DA가 있고, 중간에는 TSV라는게 있어서 위 Core die와 연결되게 됩니다. 이때 TSV는 FAB에서 ETCH를 엄청많이 해서 실리콘 웨이퍼를 관통(실제로는 절반정도만 관통하고 Metal 배선으로 연결합니다)하고 서로 다른 Chip가 연결됩니다. 이때 연결시키는건 Microbump라는 비유하자면 납땜의 납으로 연결시켜주는 방식으로 진행됩니다.

'메모리' 카테고리의 다른 글

| DRAM 디램 공정 (10) | 2022.03.14 |

|---|---|

| DRAM 디램 소자 동작 및 구성 (3) | 2022.03.14 |