안녕하세요? 여기선 DRAM 소자와 공정에 대해 포스팅해 보겠습니다! 면접이나 업무 보실 때 참고하세요~

다 보시고 "DRAM 디램 소자 동작 및 구성"도 보시면 재미있을 겁니다.

DRAM을 제작하는 공정에 대해 알아보겠습니다.

메모리의 용량을 높이려면, 한정된 공간에 많은 수의 메모리를 욱여넣어야 합니다. 그렇다면 가장 많이 욱여넣을 수 있는 구조는 무엇일까요? 바로 아래 그림처럼 트랜지스터를 합쳐 신호 선을 공유하면 됩니다.

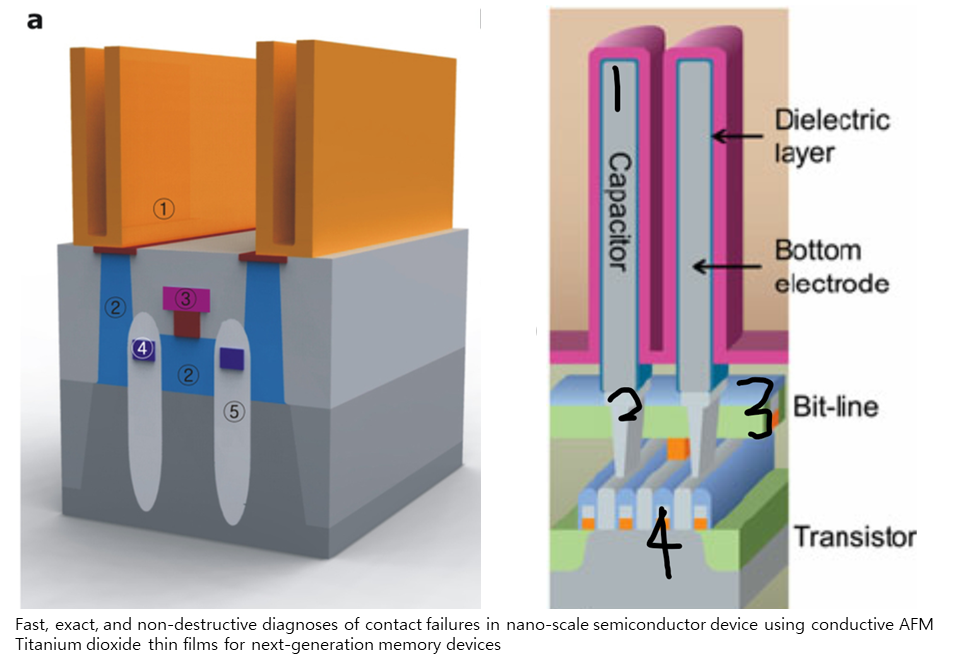

DRAM 소자에는 두개의 선이 필요합니다. Word line(WL)과 Bit line(BL)입니다. 앞선 포스팅에서 DRAM은 한 개의 bit line을 두 개의 트랜지스터가 공유한다고 하였습니다. 위 그림에서 왼쪽은 우리가 익히 아는 DRAM 구조이고 중간이 실제 사용하는 DRAM입니다. 크기를 축소하기 위해 Bit line을 두 트랜지스터가 공유하는 모습입니다.

이 회로를 공정하기 위해선 오른쪽 그림으로 구성해야 합니다. 중간에 큰 BL이 하나 지나가고, 그 옆에 WL 두 개가 지나가고 끝에 커패시터와 GND가 있는 구조입니다. BL 이 Drain, WL이 Gate, Capacitor가 Source인 트랜지스터 2개가 탄생하게 됩니다. 앞으로 오른쪽 그림을 영어로 '구분'이라는 의미의 Isolation이라 부르겠습니다.(사실 Isolation은 저 타원 부분인데, 설명을 위해 부르겠습니다)

저걸 조금 더 고급스럽게 그리면 아래쪽 그림처럼 됩니다.

왼쪽 그림에서 3번 분홍색이 BL이고 4번 보라색이 WL입니다. 놀랍게도 5번이 트랜지스터입니다. 단순하게 하기 위해 BL과 WL은 직각으로 배치하는데, 오른쪽 그림처럼 위에서 BL은 가로로, WL은 아래에서 세로로 배치됩니다. 이 line이 연결되는 곳에 바로 트랜지스터가 형성되는데, 사이즈가 점점 줄어들게 되어서 Short channel effect가 발생하게 됩니다. 따라서 채널길이를 길게 하기 위해 채널을 아래로 파게 됩니다. 즉 왼쪽 그림의 5번이 gate가 되고 인접한 회색이 channel이 되게 됩니다. 이를 recess gate 트랜지스터라 하며, DRAM소자에서만 사용되게 됩니다. 이는 2030년 이전 메모리 구조이고, 향후 10년 후에는 VCT과 같은 다양한 구조의 Cell Transistor가 등장 할것으로 보입니다. (VCT (Vertical Channel Transistor, 3D DRAM)에 대한 내용이 궁금하시다면 들어가보세요) (Cell 외 다른 부분은 Planer Transistor나 파운드리에서 사용하는 Transistor를 사용합니다.-사실 메모리 제품에서는 공정 nm가 낮다고 큰 이득이 없어 조금 지난 파운드리에서 사용하는 TR을 사용합니다.)

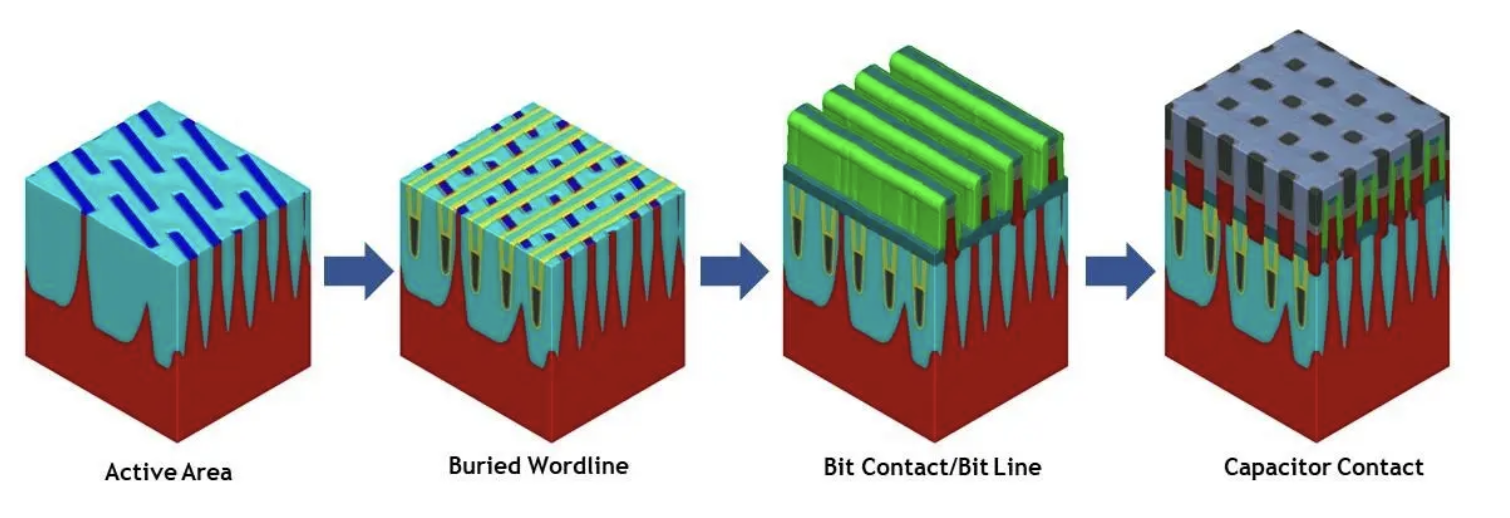

위 그림은 앞으로 설명할 공정 단계를 표기해둔 내용입니다. 본 포스팅 처음에 다루었던 모습과 사뭇 동떨어진 모습이지만, Active Area의 파란색이 본 포스팅 가장 첫 그림의 타원 구조이고 Buried Wordline에서 쑥 들어간 부분이 Transistor하나 입니다.(파란 타원에 쑥들어가는게 두개인게 본 포스팅 첫 그림과 같죠?) Bit Line은 Wordline과 수직하게 배치되고, Bit Line과 Wordlined을 다 쓰고 남은자리에 Capacitor가 배치되게 됩니다. 이제 이들을 하나하나 잘라서 살펴보겠습니다.

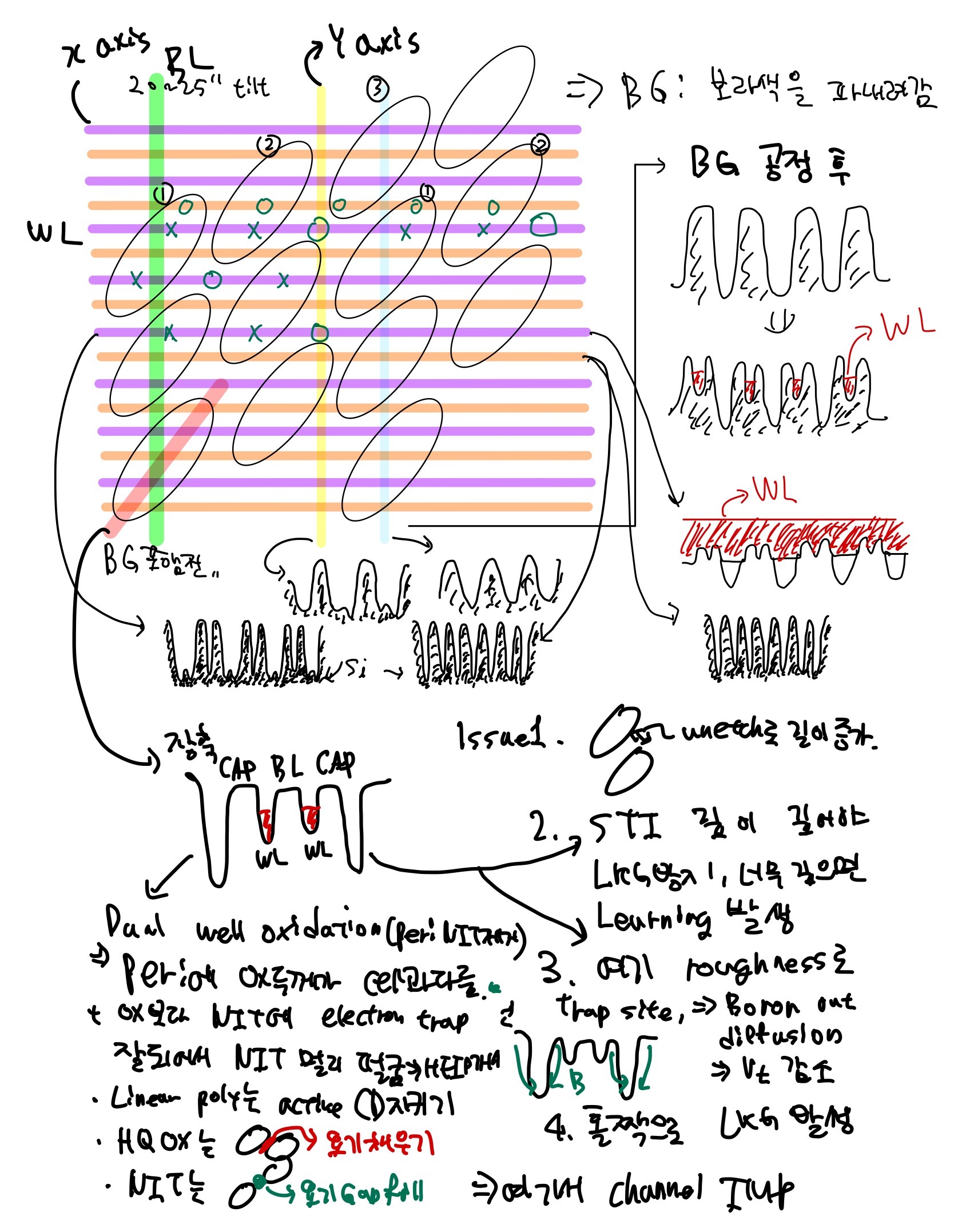

먼저 위 그림에서 가장 핵심이 되는 Word Line(WL)과 Bit Line(BL)을 배치해보겠습니다. 핵심은 한정된 영역에 가장 많은 소자를 우겨넣기 입니다. 먼저 BL과 WL먼저 배치해 보겠습니다. 앞서 복잡성을 줄이기 위해 BL과 WL은 직각으로 배치하기로 하였으므로 왼쪽 그림처럼, 초록색과 보라색 노란색 파란색 과같은 line을 막 배치합니다.(초록 파랑이 BL, 보라 주황이 WL). 이때 엄청 많이 욱여넣어야 하므로 Isolation을 살짝 비스듬하게 배치합니다. 왼쪽 그림에 타원이 옆으로 뉘어있는 것인데, 보통 20~25도 정도 누워있습니다. 이게 가장 많이 욱여넣을 수 있고, 다른 말로 허니컴 구조라고도합니다.(벌집모양 구조라고 하는 건데, 그거 생각하면 더 이해 안 되니 단어만 기억해 주세요~)

저 검은색 타원에만 실리콘이 있고 나머지는 다 빈 공간이 됩니다. 다른 소자로 분리시키는 기본적인 부분입니다. 분리시킨다 하여 ISOLATION이라 하고 이를 제작하는걸 ISO 공정이라 고합니다.

1. ISO 공정

간단히 타원 부분을 남기고 모조리 Etch 공정으로 물질을 없애면 됩니다. 파낸 부분을 Trench라 하고 STI(Shallow trench isolation)라고도 부릅니다. 타원이 옆으로 누웠으므로 x방향과 y방향 단면으로 여러 개의 iso를 본다면 본다면 모양이 여러 가지로 나옵니다.(최대한 상상력을 살려보면 좋습니다.) 타원(실리콘 남은 부분)을 남겨두곤 파인 거여서 각 가로 세로 선에 대해 화살표로 연결된 그림처럼 단면이 생기게 됩니다. 별 의미 없는 그림 같지만 뒤로 갈수록 정말 중요한 그림입니다.

보라색과, 초록색 선이 있는데, 보라색은 WL, 초록색은 BL입니다.

BL부터 보겠습니다(초록색). BL은 두 개의 트랜지스터 중간에 위치해야 하기 때문에, iso 중간을 지나야 합니다. 따라서 BL은 모든 ISO 중간을 관통합니다. 따라서 기울어진 ISO는 BL을 기준으로 배치되는 것을 확인할 수 있습니다.

WL은 트랜지스터 gate를 지나야 합니다(보라색). 따라서 타원의 2/5와 4/5 지점에 배치되어야 하므로 x로 표시된 부분을 기준으로 가로 방향으로 관통해서 갑니다.

마지막으로 트랜지스터 끝에 커패시터와 GND가 있어야 합니다. 1/5 부분과 5/5 부분에 커패시터가 배치되는데, 어차피 GND로 연결되므로 별다른 line이 필요하진 않습니다. 이 부분을 SN이라고 합니다.

ISO 공정에서는 ISO 간 사이가 잘 파이지 않아 두 ISO 사이의 거리를 증가시키는 방법, 즉 ISO자체의 크기를 줄이는 공정이 들어갈 수 있습니다. 하지만 ISO자체가 작아지면 나중에 BL, WL, 커패시터 간의 간격을 욱여넣기 어려워집니다. 또한 STI의 길이가 깊어야 서로 간의 간섭을 안 하는데, 너무 깊어지면 위치에너지가 높아져 기둥이 옆으로 쓰러질 수도 있습니다.

2. WL 공정

ISO 공정이 끝나면 다음으로 WL을 만드는 공정을 합니다. 위 그림에서 보라색 선인데요. 보라색 부분을 Etch를 하여 어느 정도만 실리콘을 없애줍니다. 없애주고 난 뒤의 모양을 살펴본다면, 타원의 장축으로(x축에서 20도 정도) 잘라본다면 깊게 파인 두 개 홈 사이에 작게 파인 두 개 홈이 남습니다. Etch 한 부분에 전극을 증착시켜 준다면, 작은 홈에 빨간색으로 되어있는 전극을 만들어집니다.(계속 위에 있는 그림을 보세요!)

y축으로 본다면 ISO 중간에 전극이 배치된 것으로 보이고, x축으로 본다면 전극이 쭉 연결된 것으로 보입니다.

쭉 연결된 부분만 다시 보겠습니다. 왼쪽그림인데요. 위에 그렸던 x축으로 잘랐을 때 그림입니다.(WL을 따라)

빨간색이 트랜지스터 gate를 금속으로 연결시켜 주는 전극 WL입니다. 파란색이 앞서 말했던 STI입니다.(ISO 간 분리시켜 주는 절연) 낙타 등처럼 뽈록뽈록 튀어나와 있는 한 개의 뽈록이 ISO 하나입니다. 다시 말해 뽈록 하나가 트랜지스터 하나의 gate부분이라고 생각하시면 됩니다. 그렇게 ISO 두 개를 거쳐 STI을 지나 다시 ISO 두 개를 지나는 형태로 되어있습니다. 맨 끝에서 WL의 전극을 다른 곳으로 빼주기 위해 Peri 쪽으로 많이 빼줍니다.(Peri에 대한 설명은 전 포스팅에서) 이때 Peri는 ISO etch가 되지 않아서 경계에서 높이 차이가 발생할 수 있어, WL인 끊길 수도 있습니다.

여기서 트랜지스터는 언제 만드냐고 궁금해하실 수 있는데, WL을 형성하기 위해 ETCH를 할 때 Doping을 하고 Gate oxide를 만드는 공정을 하여 형성합니다. 이때 peri와 회로 부분의 트랜지스터까지 같이 만듭니다.

y axis로 보면 트랜지스터 gate에 빨간색 WL이 들어가 있는 것을 볼 수 있습니다. x axis에 뽈록한 부분이 y axis 가장 중간 아래 파란색 oxide 부분이고, WL이 그 위에 채워집니다. WL 물질은 보통 TiN로 감싼 W을 사용하는데, Oxide 보호, 저항 감소등 다양한 이유가 있습니다.(자세한 원리는 다음 포스팅에서 이어가겠습니다.) gate를 만들었으면 poly와 여타 다른 절연 물질로 막아놓습니다. 다음공정을 진행하기 위해 물질을 높게 쌓아놓고 CMP로 평평하게 만들어 놓고 BL공정으로 들어갑니다.

3. BL 공정

이제 BL을 깔아야 하는데, 이미 WL을 깔기 위해 이것저것 etch 하고 물질을 쌓고 했기 때문에 이들과 간섭을 최소화하기 때문에 땅속에 빨대를 꽂아 석유를 뽑아내는 것처럼 전극을 연결시켜 줍니다. 이때 정확히 어떤 지점에 빨대가 닿기 위해서 Contact이라는 공정을 해야 합니다. 이제부터는 이런 이유로 모든 부분에 Contact이라는 공정이 추가됩니다. BL의 경우 Bit line contact(BLC), Storage node(SN)의 경우 SNC(Storage node contact)이고 뒤에 metal 공정은 Metal contact 등 꼭 추가됩니다. 소자 공정 실패가 가장 많이 일어나는 것도 이 Contact인데요. 위에서 쭉 내려올 때 contact가 딱 만나야하기 때문입니다.

위 그림에서 Contact들이 어디에 있는지 딱 보입니다. DRAM은 Gate를 먼저 만들고 BLC를 만든 뒤 BL을 만들고 SNC를 만들고 SN을 만드는 순서로 진행합니다. BLC는 WL과 WL사이에, 다시 말해 ISO 중간에 형성됩니다. 위 그림에서도 Gate와 Gate 사이에 BL이 만들어지는 걸 볼 수 있습니다.

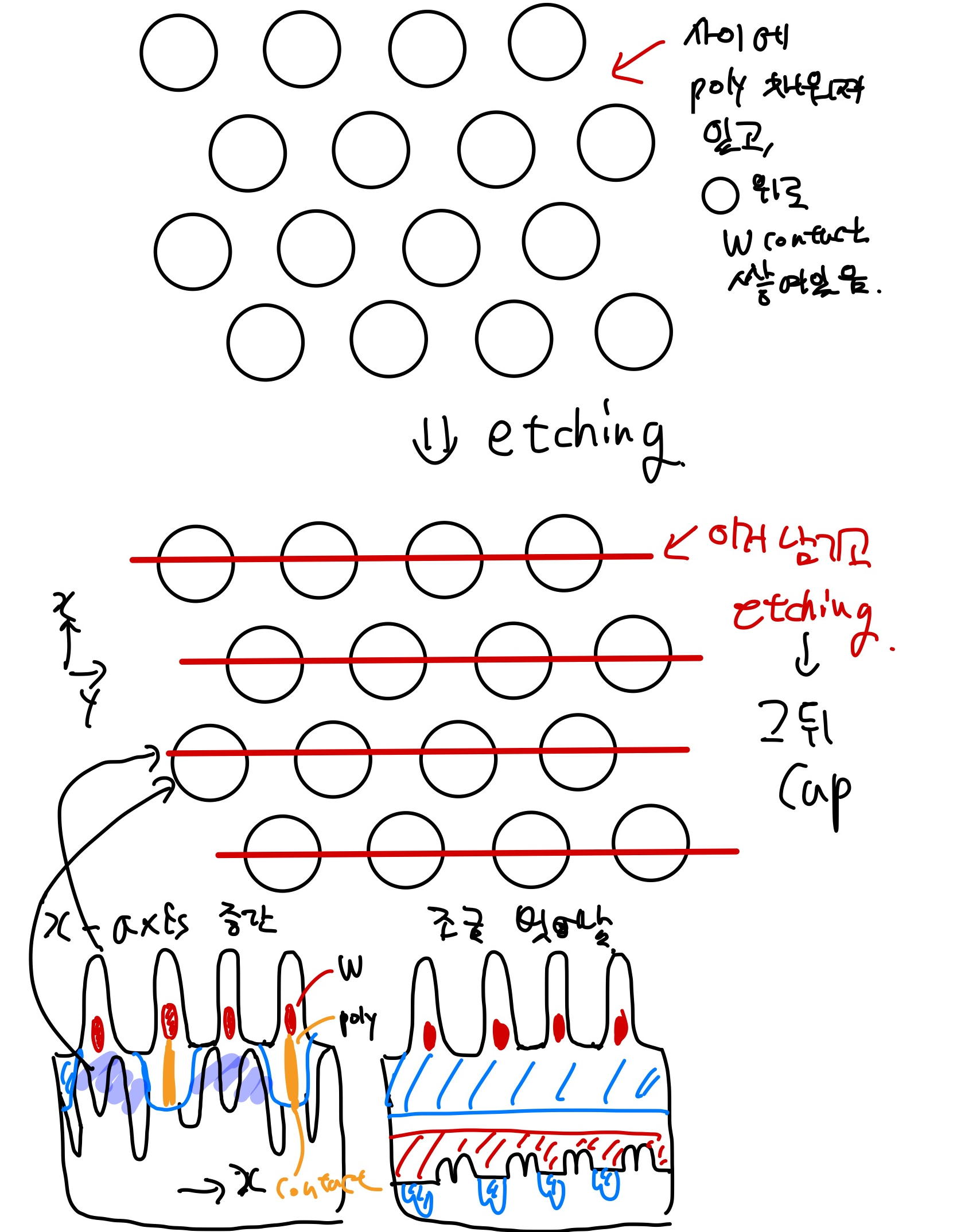

이해를 돕기 위해 BLC를 만들 부분을 위에서 보겠습니다. 위에서 본다면 위 사진과 같이 ISO(파란 타원) 중간에 빨간 동그라미처럼 만드는 게 BLC입니다. 이를 만들 때 인접한 ISO의 SN 부분과 닿을 수 있으니 주의하여 제작해야 합니다.

처음 하는 공정은 파티션을 만들고 이 파티션에서 생성된 oxide를 mask로 이용해 중간 부분을 형성하는 방법입니다.

아까 배선도에서 x방향으로 잘라본다면(WL형성되는 방향) WL이 쭉 만들어져 있기 때문에, WL 피해서 BL을 만들어야 합니다. 다시 말해 WL과 WL 사이에 BLC를 만들 곳을 생각해 둡니다. 왼쪽 그림의 작은 뽈록이(빨간색으로 채워진 곳 아래)가 WL이 존재하는 ISO라고 했습니다.(다시 말해 ISO를 반 자른단면입니다.) 이 뽈록이의 중간과 BLC가 잘 만날 수 있게 물질을 ETCH해 둡니다. 이렇게 ETCH한 결과 왼쪽 그림처럼 됩니다. 다시말해 들어간 부분에 BLC가 형성되고, 튀어나온 건 절연 부분입니다.

이걸 y 방향, WL과 수직 하게 보면 빨간색 WL사이에 움푹 들어간 부분이 있는데, 이 부분에 BLC가 형성될 겁니다.

이해를 돕기 위해 소자를 위해서 바라보겠습니다. 방금 만든 거에서(왼쪽그림) 솟아나온 부분을 이제 원으로 표현하고 아래 그림에 표현해 보겠습니다

원들이 현성되어 있는데, 이 원 사이사이의 공간이 BLC가 될 예정입니다. 따라서 아래 그림 빨간 선처럼 BL을 만들 부분을 남기고 ETCH를 한 뒤 절연 물질을 채워 절연하게 됩니다. (아직 BL이 형성된 건 아닙니다.)

4. SNC 공정(BL 형성 후 )

이제 원통형 빈 공간 빨간 선이 지나 간자리에 BLC를 형성할 전도 물질을 삽입하고 그 위에 빨간색 지나간 자리에 BL을 형성하는 도체를 삽입합니다. 완성하고 위에서 보면 BL이 형성되는 것을 볼 수 있습니다.

만들고자 한 소자는 SNC-BG-BLC-BG-SNC로 이루어져 있는데, BLC를 형성했으니 이제 SNC를 형성해야 합니다. SNC는 BL이 안 지나간 자리를 가지고 만들 것으로 BL과 수직 하게 먼저 위치를 지정해 줍니다.

왼쪽 파란 선을 따라 SN을 형성할 자리를 ETCH 하여 SNC 자리를 만들어줍니다. 이따 SNC를 형성하는 공정이 Peri부의 트랜지스터의 Contact 부분을 형성하는 공정과 같아 동시에 진행해 줍니다.

따라서 SNC로 사용하기 위해 파낸 부분에 전도 물질을 넣어주고 이제 SN을 형성하기 위해 W을 쌓아줍니다.

4. SN 공정

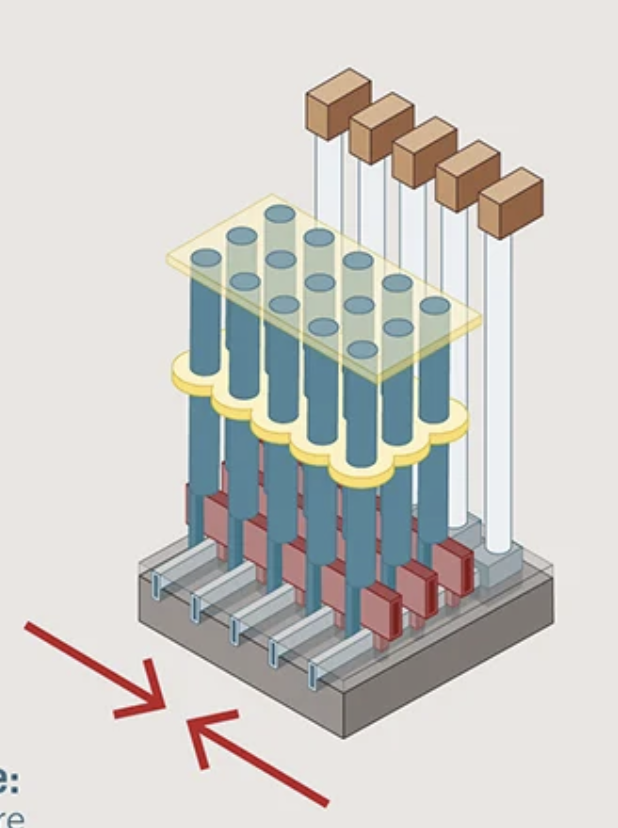

SN(커패시터)는 아주 높고 얇게 만들어지기 때문에 틀을 만들어주는 물질을 다 쌓고 파내고 절연물질을 채워주고 전극을 달아주는 형식으로 진행합니다. 따라서 틀을 만들어주는 Oxide 계열의 물질을 쌓아주는데, Etch rate(식각 속도)가 빠른걸 아래로 느린 걸 위로 쌓아주며, 이게 너무 길고 얇게 형성되어 쓰러질 수 있기 때문에, 지지대로 중간중간 지지해 주는 물질을 만들어줍니다.

다 쌓은 다음, SN을 형성할 곳에 구멍을 뚫어 내부 물질을 다 빼내고 유전체를 주입해 줍니다.

그러면 커패시터가 완성이 됩니다. 사실 Storage Node의 경우 기술이 발전함에 따라 끊임 없이 발전합니다. 따라서 현재도 이 포스팅(이미 알려진) 기술 외 다른 기술이 사용될 가능성이 있습니다. 다만 Storage Node의 핵심은 이미 Transistor로 향하는 전극은 존재하고, 절연체를 만들어놓고 식각한 뒤 절연체 형성 후 전극을 다시 만드는 형식으로 진행된다는 점입니다. Capatior는 전극과 절연물질이 무조건 필요하기 때문입니다. 물론 Capacitorless DRAM이 제안되고 있긴 합니다.

지금까지 BL에서 오는 신호를 트랜지스터를 통해 커패시터로 도달하는 것까지를 만들었습니다. 이제 커패시터(SN)의 Ground를 만들어야 하는데, 모든 Ground는 연결되어 있어도 됩니다. 따라서 제작한 SN위를 모두 절연 물질로 덮어 연결시켜 줍니다. 이를 Plate라 부르며 아래 그림의 SiGe, W/WN)로 표기된 부분입니다.

여기까지가 DRAM의 Cell을 만드는 방법이고 물질과 디테일한 공정은 회사마다 모두 다르게 됩니다.

이후에는 여느 반도체 공정과 같게 배선이 시작됩니다. 회로도에 맞게 Metal 배선을 위한 Photo 공정 및 Etch공정이 동반되고, 절연물질이 쌓이고 다시 Metal 배선을 위한 Photo 공정 및 Etch 공정이 반복됩니다. 이후에 내용은 DRAM에만 국한된 내용이 아니므로 생략하도록하겠습니다. (굳이 비슷한 공정을 찾는다면 위 SNC공정을 참조 부탁드립니다.)

'메모리' 카테고리의 다른 글

| HBM (High Bandwidth Memory) (0) | 2024.05.12 |

|---|---|

| DRAM 디램 소자 동작 및 구성 (3) | 2022.03.14 |